本博客是物联网安全系列的一部分,我们将讨论有关物联网/工业物联网生态系统及其安全性的基本概念。如果你还没有看过该系列的前几篇博客,我会敦促你先看一遍。如果您只对硬件JTAG、SWD感兴趣,请随时继续。 2023-11-6 09:46:6 Author: 安全狗的自我修养(查看原文) 阅读量:52 收藏

本博客是物联网安全系列的一部分,我们将讨论有关物联网/工业物联网生态系统及其安全性的基本概念。如果你还没有看过该系列的前几篇博客,我会敦促你先看一遍。如果您只对硬件JTAG、SWD感兴趣,请随时继续。

物联网安全-5.ZigBee协议物联网安全-6.ZigBee安全物联网安全-7.物联网固件逆向

目录

如果您是硬件黑客的初学者,并正在寻找一些要点,那么本博客系列可以为您提供帮助。我们在 IoT 攻击面博客中讨论了 JTAG 和 SWD 作为硬件攻击面。在这篇博客中,我们将详细讨论它们。除了基本介绍外,我们还将讨论可能的攻击场景、工具和方法,如果您能够访问硬件上的JTAG/SWD接口,您可以使用这些场景、工具和方法来攻击设备。因此,如果您不熟悉它并想开始使用,请继续关注:)。

介绍

JTAG的

JTAG(联合测试行动小组)是一项行业标准,由联合(欧洲)测试访问小组协会于 1985 年制定。它最初是为验证印刷电路板 (PCB) 的设计和测试而开发的。1990 年晚些时候,它被标准化为 IEEE 标准 1149.1-1990,作为标准测试访问端口和边界扫描架构。最初,随着集成电路的发明,复杂性的增加、密度的增加和组件的更小,测试PCB上的物理互连并不容易。JTAG边界扫描作为一种解决方案,通过将物理访问限制在少数几个信号上来执行芯片物理互连的测试和调试。如今,JTAG被用于许多其他应用,包括在线调试,无需直接从外部访问系统地址或数据总线即可与芯片内的存储器/寄存器进行通信,以及用于编程设备。下图显示了JTAG芯片的架构(来源 - 这里)。

JTAG芯片由将芯片连接到PCB的逻辑单元或边界扫描单元组成。它们可以从引脚或内核逻辑信号捕获数据,并将数据发送到引脚上。这些逻辑单元可通过串行测试数据输入 (TDI) 和测试数据输出 (TDO) 接口访问。测试控制器提供逻辑访问的主要接口是测试访问端口(TAP),由4个必需信号和一个可选的复位信号组成。

TCK (Test Clk) – 测试时钟同步内部状态机的操作。JTAG标准没有规定实际的时钟速度。

TMS(测试模式选择) – 它控制JTAG状态机。它在 TCK 的上升沿进行采样,以确定状态机的下一个状态。

TDI(测试数据输入) – 将数据发送到芯片中。当内部状态机处于正确状态时,它会在 TCK 的上升沿进行采样。

TDO (Test Data Out) – 从芯片输出的数据。当内部状态机处于正确状态时,它在 TCK 的下降沿上有效。

TRST(测试重置:可选)— 重置 TAP 控制器状态机。

根据 IEEE-1149.1 标准的定义,TAP 控制器使用由 TCK 和 TMS 信号控制的 16 态有限状态机。TMS 在 TCK 上升沿的状态决定了向下一个状态的过渡。每个JTAG TAP都有一个指令寄存器(IR)和一个数据寄存器(DR)。这些寄存器的大小是可变的。状态机通过 IR 选择操作/指令,并通过 DR 传递参数或数据更新。状态机的详细工作可以从参考文献 [1] 中读取。

JTAG规范没有为连接器设计定义的协议。JTAG连接器的引脚接口数量有6、10、14、16、20等。除了 4 个 JTAG 信号外,这些连接器还可以有额外的信号。如下图所示(来源 – 参考 [1])

为了通过JTAG接口与器件通信,我们必须识别通过TAP与JTAG芯片状态机通信的4个JTAG信号TCK、TMS、TDI和TDO。也可以通过菊花链连接多个JTAG芯片来与它们进行通信,如下图所示(来源 - 维基百科上的数据)

有一种引脚数较少的JTAG,称为紧凑型JTAG(cJTAG),它只有两个引脚,TMSC(测试串行数据)和TCKC(测试时钟)。它被定义为 IEEE 1149.7 标准的一部分。JTAG规范定义了一些强制性的边界扫描相关指令和一些可选指令。但是,用于调试应用程序(而不是边界扫描)的 TAP 通常对与边界扫描相关的这些强制指令提供最少的支持或不支持。两个重要的说明是:

旁路 – TDI 和 TDO 连接到单位数据寄存器(也称为旁路)。该指令允许器件被绕过,同时允许串行数据通过链/扫描路径中的下一个器件。

IDCODE – 这是一个可选指令,但被广泛使用(不是普遍使用)。它与 32 位设备 ID 寄存器 (IDCODE) 相关。它包括芯片 ID,即标准化格式的制造商代码。

复位状态后,IR 预加载 BYPASS 或 IDCODE 指令。这种识别还有助于识别芯片中使用的处理器/微控制器的类型。

其他指令包括 EXTEST、SAMPLE、PRELOAD、HIGHZ、INTEST、CLAMP、RUNBIST 和 USERCODE。制造商提供的设备可能会定义更多说明。JTAG支持不同的架构,包括ARM、Atmel AVR、TI MSP430、FPGA、MIPS、CPLD等。

社署

SWD(串行线调试)通过将引脚数减少到仅两个、双向数据信号 (SWDIO) 和主机发送的时钟信号 (SWCLK) 来提供调试端口。它提供了所有正常的JTAG调试和测试功能(它不提供JTAG中的边界扫描功能)。它使用 Arm 标准双向连线协议,该协议在 Arm 调试接口 v5 中定义。它是基于 ARM 处理器的设备的标准接口。在限制引脚数至关重要的情况下,它非常有用。SWD 使用称为调试访问端口 (DAP) 的总线。DAP 有一个主站(调试端口 – DP)和一个或多个从站(接入端口 – AP)。下图显示了 SWD 架构(来源 – 参考文献 7)。

外部调试器使用调试端口 (DP) 连接到 DAP。有三个调试端口接口可用于访问 DAP。

JTAG调试端口(JTAG-DP) – 它使用标准的JTAG接口和协议

串行线调试端口 (SW-DP) – 它使用 SWD 协议

串行线/JTAG调试端口(SWJ-DP) – 它可以使用JTAG或SWD访问DAP。在这种情况下,TCK和TMS JTAG信号分别被重用为SWCLK和SWDIO信号。为了从一个接口切换到另一个接口,必须发送一个特定的序列。

社署交易分为三个阶段。

从主机发送的 8 位请求阶段

从目标发送的 3 位 ACK(确认)阶段。

数据阶段,其中最多 32 位从/传输到具有奇偶校验位的主机。

当必须更改数据方向时,将发送TRN(周转)周期。下图显示了 SWD 读取传输(来源 – 参考文献 7)。

有关JTAG和SWD接口的更多概念细节,请参阅本博客末尾提到的参考资料。在接下来的章节中,我们将讨论攻击场景和方法。

可能的攻击场景

访问硬件上的JTAG/SWD接口为攻击者闯入设备提供了许多可能性。以下是可能的攻击场景:

攻击者可以访问控制器的内部存储器,从而操纵寄存器值。操纵内部寄存器可能会产生不同的效果。例如,在某些情况下,即使实现了控制器读取保护,攻击者也可以操纵寄存器值,并且有可能绕过保护实现。同样,攻击者还可以更改设置并绕过与引导加载程序相关的保护以及开发人员可能出于安全考虑而锁定的其他关键寄存器。

通过JTAG/SWD接口访问硬件,攻击者可以调试系统。它可以帮助他/她发现更多漏洞并对设备进行攻击。为了更好地理解,您可以参考我们的博客“硬件攻击 - 堆栈粉碎和保护”。在这里,您可以了解对硬件上JTAG调试端口的访问如何帮助我们识别导致RCE(远程代码执行)的缓冲区溢出漏洞

从攻击者的角度来看,另一个最显著的优势是,对JTAG/SWD调试接口的访问为从设备中提取固件、修补固件以及将修改后的易受攻击/恶意固件重新刷新到设备中提供了可能性。访问固件为攻击者捕获和利用其他漏洞提供了巨大可能性。

执行攻击

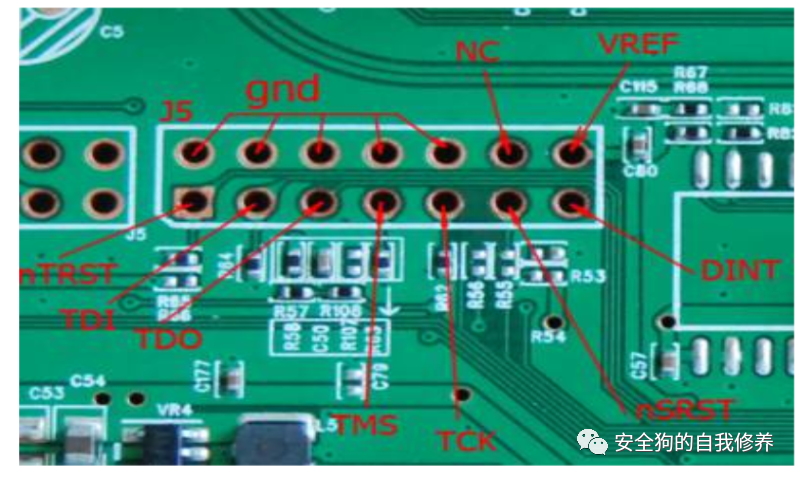

我们首先需要识别硬件上相应的端口引脚,以便通过JTAG/SWD端口与器件进行交互。下面是几张图片,显示了硬件上大多数JTAG端口测试点/引脚排列的外观。

(来源 - 这里)

(来源 - 这里)

侦察

您可以参考前面的博客“物联网安全-13 硬件分析简介”,以更好地了解硬件侦察。

情况 1:您没有实际的硬件,但您知道设备的 FCCID 编号。

转到 FCCID web网站,搜索设备的 FCCID 编号。如果正确,您将找到有关设备的所有内部图像和详细的内部外部信息。对于硬件上具有 JTAG/SWD 接口的设备,您可能会收到看到内部映像的提示。是的!!一旦您知道自己拥有攻击面,就可以获取/购买该设备并执行进一步所需的步骤来攻击该设备。

案例 2:您可以访问硬件。

一旦你拥有了物理硬件,第一步应该是执行侦察。检查印刷电路板(PCB)上的每个测试点和芯片,看看是否可以获得JTAG/SWD接口。

如上所述,对于JTAG,我们需要识别四个信号引脚(TCK、TDI、TDO、TMS)和Vcc、GND引脚。对于 SWD,我们需要两个信号引脚(SWDIO、SWCLK)和 Vcc、GND 引脚。下面提到了几种识别设备上这些接口引脚的方法:

手动识别 – 识别设备中使用的微控制器,取出其数据表,并识别微控制器的 JTAG/SWD 引脚。例如,我们将以EXPLIoT DIVA板为例。

PCB上标记为U7的diva板中使用的微控制器是STM32F411x,我们可以在其数据表中搜索具有JTAG/SWD接口连接的引脚。下图显示了数据表的该部分。

根据器件中使用的IC封装(此处为LQFP64),我们确定控制器上的JTAG端口引脚。然后,我们将万用表设置为连续模式,如下图所示:

然后,我们将一个探针放在控制器上的JTAG端口引脚上,将另一个探针放在PCB上的测试点/接头引脚上,怀疑是JTAG端口引脚。重复该测试,直到识别出引脚。识别 SWD 引脚的过程是相同的。手动识别无疑会很忙,但不用担心;我们有自动化工具来解决这个问题

自动识别 - 许多可用的工具可以帮助我们扫描和识别硬件上的JTAG/SWD引脚。

是的!!一旦在硬件上识别出JTAG/SWD接口引脚,就该闯入器件了。

EXPLIoT 总线审计器 – 它支持 JTAG、SWD、I2C、UART。它具有可调节的目标电压。JTAG和SWD接口的演示示例可以从我们的博客“物联网安全-第14部分(硬件调试端口的介绍和识别)”中理解。

JTAGEnum – 它是基于Arduino的oprn源项目。它不支持UART,也没有可调电压。使用起来更便宜。在将引脚连接到Arduino之前,请确保调整电压电平。您可以参考此处的博客,了解如何使用JATGEnum识别JTAG引脚。

JTAGulator – 它支持 JTAG、UART、SWD。它具有可调节的目标电压。您可以参考此处的博客,了解如何使用JTAGulator识别JTAG引脚。 注意:在将任何外部设备连接到目标板之前,请确保调整电压电平并使攻击/扫描设备和目标设备的接地通用。

嗅探通信

逻辑分析器等工具可用于嗅探具有JTAG/SWD接口的器件与控制器之间的通信。逻辑分析仪将显示JTAG端口的TCK、TDI、TDO、TMS信号线或SWD端口的SWCLK、SWDIO线。Saleae Logic Analyzer、PulseView 等软件具有检测这些信号的功能,可直接向您显示解码后的数据以及相应的 JTAG/SWD 接口。嗅探通信可以帮助解码 ID 代码和其他敏感信息。

接口

为了与器件上的JTAG/SWD接口进行通信,我们需要一个协议适配器和一个软件,该软件可以通过适配器通过JTAG/SWD与器件进行通信。再次记下重要的一点,“在将任何外部设备/适配器连接到目标板之前,请确保调整电压电平并使攻击/扫描设备和目标设备的接地通用。有多种适配器可用于连接JTAG/SWD接口。下面提到了其中的一些。

EXPLIoT 纳米

巴士海盗

希克拉

为了通过这些协议适配器与主机进行JTAG/SWD接口通信,我们需要一些可以通过主机从用户那里获取指令,并通过协议适配器将相应的低级指令发送到相应的JTAG/SWD接口的东西,反之亦然。Openocd:Open on-Chip Debugger 是一款调试软件,通过 JTAG/SWD 接口的分层架构和 TAP 支持提供片上编程和调试支持。它支持调试目标(例如 ARM、MIPS):单步、断点/观察点等。它支持各种芯片、接口和目标。它还打开 GDB 和 telnet 服务器。您可以在硬件上执行 GDB 调试,或使用 openocd 命令通过 telnet 进行通信。为了与相应的芯片和接口进行通信,我们需要提供正确的配置文件,以及我们正在使用的芯片和接口。下面,我们将展示在目标EXPLIoT DIVA板上使用EXPLIoT Nano的JTAG接口。

通过上述任何扫描工具/方法识别JTAG引脚后,将JTAG引脚TCK、TMS、TDI、TDO与适配器上的相应JTAG引脚连接(此处,EXPLIoT Nano根据其数据表/用户手册)。连接图像如下所示。

现在,为了与JTAG接口进行通信,我们需要启动Openocd。$ openocd -f expliot_nano_jtag.cfg

注意 – 我们将配置文件传递给 openocd,使其了解目标微控制器和使用的调试适配器。对于不同的微控制器、适配器配置,您可能需要选择相应的配置文件。有关 openocd 配置文件的更多信息,可以在这里

阅读:与接口的通信开始如下图所示。

现在,在另一个终端中,我们将打开telnet并通过JTAG接口执行不同的操作。此处的链接详细描述了用于执行不同操作的命令,包括内存读取、写入、转储等。

因此,例如,要提取固件,命令是,dump_image flash_dump.bin <address> <flash memory length>

我们首先需要确定我们正在使用的芯片的闪存的地址和长度。如上所述,EXPLIoT DIVA板具有STM32F411x微控制器。我们检查其数据表,我们确定了0x8000000和长度的闪存地址,0x807FFFF – 0X8000000 = 7FFFF,如下图所示。

通过telnet,我们发送以下命令,

停

dump_image flash_dump.bin 0x8000000 0x7FFFF

恢复

它成功从设备中提取固件,如下所示。

因此,可以使用各种 openocd 命令来执行各种操作,包括操作寄存器值、修补固件等。类似的方法适用于 SWD 接口,我们只需要连接相应的 SWD 引脚,并在配置文件中提及相应的 SWD 传输。因此,一旦我们成功地与JTAG/SWD端口进行连接和通信,它就为各种攻击场景提供了可能性,如上所述。在以后的博客中,我们将对某些物联网设备进行这些攻击,敬请期待。

结论

测试

在这篇博客中,我们了解了JTAG、SWD接口、攻击场景的可能性以及攻击方法。我们希望您喜欢并从中获得一些有价值的信息。这些工具和攻击方法可以让你对在硬件上发现JTAG/SWD接口并用它来攻击某些设备时该怎么做有一个基本的了解。

引用

[1] https://blog.senr.io/blog/jtag-explained

[2] https://embeddedbits.org/2020-02-20-extracting-firmware-from-devices-using-jtag/

[3] https://en.wikipedia.org/wiki/JTAG

[4] https://www.corelis.com/educationdownload/JTAG-Tutorial.pdf

[5] https://developer.arm.com/architectures/cpu-architecture/debug-visibility-and-trace/coresight-architecture/serial-wire-debug

[6] https://www.cnblogs.com/shangdawei/p/4748751.html

[7] https://research.kudelskisecurity.com/2019/05/16/swd-arms-alternative-to-jtag/

其它课程

windows网络安全一防火墙

windows文件过滤(更新完成)

USB过滤(更新完成)

游戏安全(更新中)

二进制漏洞(更新中)

ios逆向

还有很多免费教程(限学员)

更多详细内容添加作者微信

如有侵权请联系:admin#unsafe.sh