嗯,用户让我用中文总结这篇文章,控制在100字以内,而且不需要特定的开头。首先,我得通读整篇文章,抓住主要内容。 文章讲的是一个NFC抓包项目的开发过程。作者从需求出发,设计了一个低成本的硬件原型,使用了ST25R3916B和ESP32-S3。硬件部分用了4层板和0402封装,成本不到50元。软件方面实现了底层射频控制和协议分析,支持完整的APDU抓取,并计划开源代码。 我需要把这些要点浓缩到100字以内。先确定主要信息:项目目标、技术实现、硬件设计、软件功能、成本和开源计划。 然后组织语言,确保简洁明了。比如:“介绍了一个基于ST25R3916B和ESP32-S3的低成本NFC抓包项目,支持ISO/IEC 14443-A协议的双向帧捕获和完整APDU交换记录。”这样涵盖了技术和功能。 再补充硬件部分:“硬件采用4层PCB和0402封装设计,成本控制在50元以内。”最后提到开源:“代码即将开源。” 综合起来,确保在100字以内,并且信息全面准确。 </think> 介绍了一个基于ST25R3916B和ESP32-S3的低成本NFC抓包项目,支持ISO/IEC 14443-A协议的双向帧捕获和完整APDU交换记录。硬件采用4层PCB和0402封装设计,成本控制在50元以内。代码即将开源。 2025-10-13 14:26:46 Author: www.freebuf.com(查看原文) 阅读量:57 收藏

作者:hediandian

状态:先行技术博客 · 项目代码整理中 · 硬件原型已验证

目标协议:ISO/IEC 14443-A(NFC-A)

关键词:NFC 抓包、协议分析、ST25R3916B、ESP32-S3、开源硬件、14443-A、低成本

0x00 起源:那个深夜的 NFC 渗透测试

凌晨 2:17,城市早已沉睡,只有写字楼的门禁系统还在忠实地工作。

我站在公司楼下,手里攥着一张从垃圾桶里捡来的员工卡——它看起来和普通工牌无异,但我知道,这张卡背后藏着整个办公区的通行权限。我的目标很简单:在不触发警报的前提下,复制它的行为,或者至少搞清楚它说了什么。

我把卡靠近读卡器,绿灯亮起,门开了。

但问题来了:它到底说了什么?

是 UID?是加密认证?还是某种动态令牌?

没有原始通信数据,我就像一个站在玻璃墙外的窃听者——看得见动作,听不见对话。

我掏出 Proxmark3,运行 hf 14a snoop,结果只抓到半截 ATQA;

换 ChameleonMini,只能模拟已知卡片,无法记录未知交互;

ACR1252U?它连原始帧都不给你。

那一刻我意识到:真正的渗透测试,需要真正的“耳朵”。

于是,我决定自己造一个——一个能完整记录 NFC-A 通信全过程的硬件。

现在,它能跑了。

0x01 我们做了什么:从射频底层重构抓包逻辑

这个项目的核心,不是依赖某个芯片的“神奇功能”,而是基于 ST25R3916B 的底层射频能力,从零实现 ISO/IEC 14443-3 层的数据透传机制。

具体来说:

利用 ST25R3916B 强大的模拟前端,直接控制载波生成、ASK 调制与解调;

通过定制 RF 库(基于 ST 官方驱动深度修改),在 PCD 发起通信时精准切换接收状态;

同时捕获两个方向的数据:

PCD → PICC:通过检测读卡器对载波的调制边带;

PICC → PCD:通过监听卡片的负载调制响应;

将原始帧通过高速 SPI 传给 ESP32-S3,再经 USB CDC 实时输出。

这并非“监听模式”,而是一套高精度、低延迟的双向帧捕获系统。

它不参与认证、不发送 ACK、不干扰原通信——只安静地记录。

0x02 硬件设计:4 层板 + 042 封装 + 不到 50 元

为了兼顾性能与成本,我们在硬件上做了大量优化:

关键规格

主控:ESP32-S3-WROOM-1(USB OTG 原生支持,双核处理 RF 与 USB)

NFC 前端:ST25R3916B(支持 106–848 kbps ASK,高灵敏度接收)

PCB:4 层板(嘉立创 EDA 绘制),L2 为完整地平面,保障射频稳定性

封装:全部采用 0402 封装元器件,在 52mm × 28mm 的板面上实现高密度布局

天线:50mm × 25mm 平面线圈,匹配网络可调,有效距离达 4–5cm

接口:USB-C 供电 + 数据,无需额外串口芯片

成本控制到极致

| 部件 | 单价(批量) |

|---|---|

| ESP32-S3-WROOM-1 | ¥22 |

| ST25R3916B | ¥24 |

| 0402 无源器件 | ¥3 |

| USB-C + LDO | ¥1 |

| 总计 | < ¥50 |

整机 BOM 成本不到 50 元人民币。这意味着,一个学生用半个月饭钱,就能拥有一台具备完整 NFC-A 抓包能力的硬件设备。

0x03 当前能力:v0.1 已支持完整 APDU 抓取

虽然项目仍处早期,但核心功能已验证通过:

已实现

完整 NFC-A 初始化流程:REQA → ATQA → UID(7 字节)→ SAK

RATS / ATS 交换(用于高速通信协商)

完整 APDU 交换:包括 ISO/IEC 7816-4 命令与响应

双向帧标记([PCD→PICC] / [PICC→PCD])

毫秒级时间戳记录(便于基本时序分析)

USB CDC 实时输出原始帧

抓包示例(MIFARE DESFire)

[PCD → PICC] 26

[PICC → PCD] 04 00

[PCD → PICC] 93 20

[PICC → PCD] 88 12 34 56 68

[PCD → PICC] 93 70 88 12 34 56 68 12 34

[PICC → PCD] 08

[PCD → PICC] E0 80 00 00 00 # RATS

[PICC → PCD] 75 77 81 02 80 31 80 # ATS

[PCD → PICC] 90 0A 00 00 00 00 # APDU: Get Key Settings

[PICC → PCD] 00 00 91 00 # APDU Response

这意味着,你可以完整复现一次门禁认证、公交扣费或 NFC 支付的底层交互过程。

0x04 硬件预览

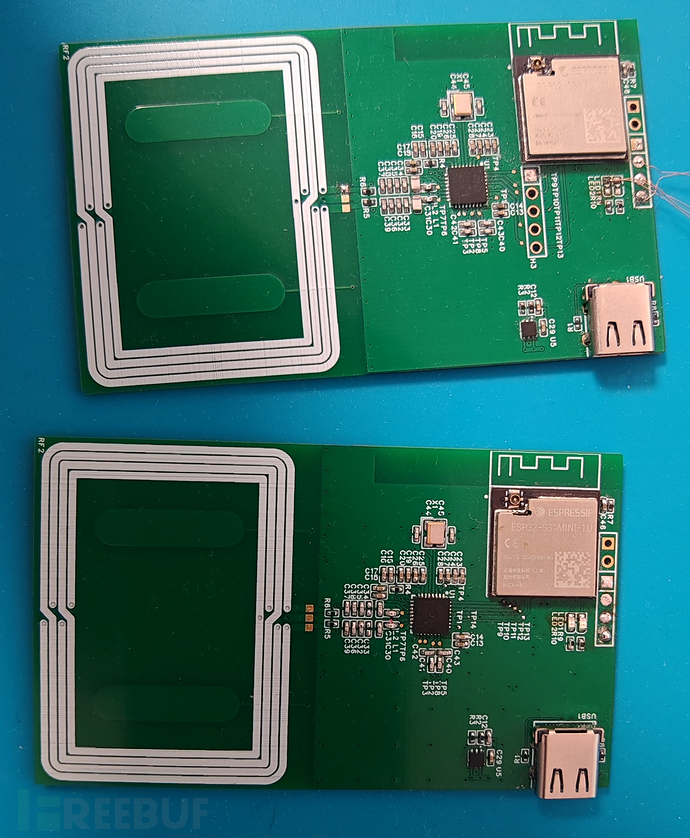

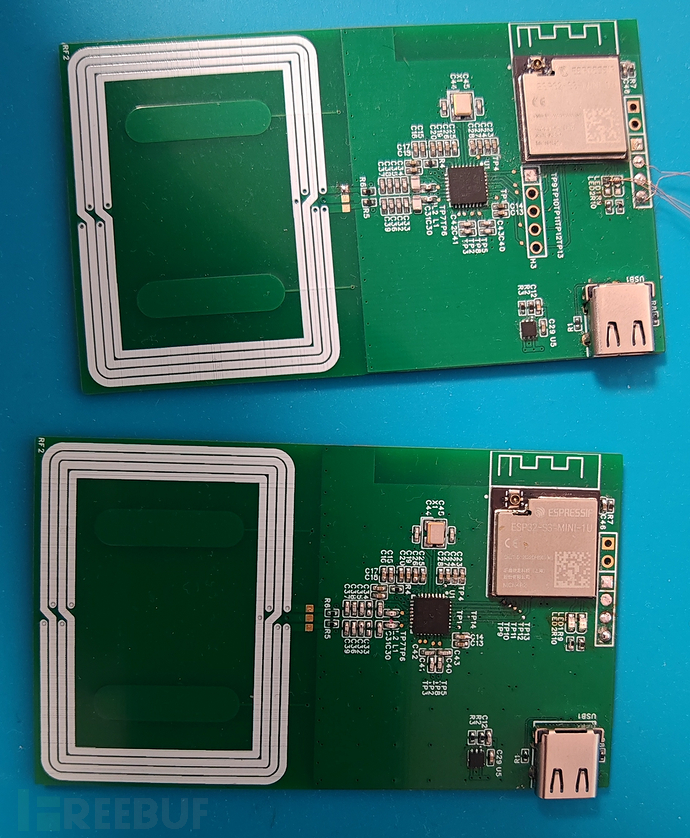

图 1:NFC Sniffer S3 原型板(4层PCB + 0402封装)

基于嘉立创 EDA 设计的 4 层板,全部采用 0402 封装元器件。尺寸仅 52×28mm,手工焊接需一定经验,但完全可行。

0x05 项目贡献:我们做了这些

这个项目通过一系列具体工作,实现了低成本、高完整度的 NFC-A 抓包能力:

1. ST25R3916B 底层 RF 库移植与增强

重写了射频控制逻辑,支持动态切换收发状态;

实现了对 14443-A 下行(PCD→PICC)和上行(PICC→PCD)的同步捕获;

优化了 FIFO 读取时序,提升高速通信下的稳定性。

2. 低成本 4 层硬件设计

使用嘉立创 EDA 完成全部设计,支持一键打样;

全板采用 0402 封装,在保证射频性能的同时压缩尺寸;

天线匹配网络可调,适配不同场景。

3. 完整协议栈抓取能力

从 REQA 到 APDU,覆盖 NFC-A 全流程;

输出带方向与时间戳的原始帧,便于后续分析。

4. 未来可扩展架构

固件支持 OTA 升级;

主动注入功能仅需软件更新,无需硬件改动;

预留 NFC-B、FeliCa 扩展接口。

0x06 下一步:代码即将开源

目前,项目代码正在紧张整理中,将尽快开源。届时将包含:

ESP-IDF 固件工程(含 RF 库、USB 驱动、抓包逻辑)

嘉立创 EDA 硬件工程(原理图 + PCB + BOM)

Python 上位机工具(实时显示 + PCAP 导出)

详细焊接与调试指南

0x07 结语:NFC?我抓。

这个项目没有宏大口号,只有一个朴素目标:让 NFC 通信可见。

我们用不到 50 元的成本,4 层 PCB,0402 封装,和一套从射频底层写起的代码,实现了对 NFC-A 全流程通信的稳定抓取。

当然,必须坦诚:这仍是一个早期原型。当前版本存在诸多不足——天线调谐依赖手动、高速通信稳定性有待验证、上行帧在强干扰环境下可能丢失、软件解析能力几乎为零……它远非完美,甚至可能在你的设备上跑不起来。

但正因如此,我才写下这篇博客。

一个人的极客实验,终将因实践而逐步完善。

NFC?我抓。

项目状态:代码整理中 · 将尽快开源

第一章完 · 敬请期待:代码开源 + 第二章《Wireshark 集成与主动注入》

如有侵权请联系:admin#unsafe.sh